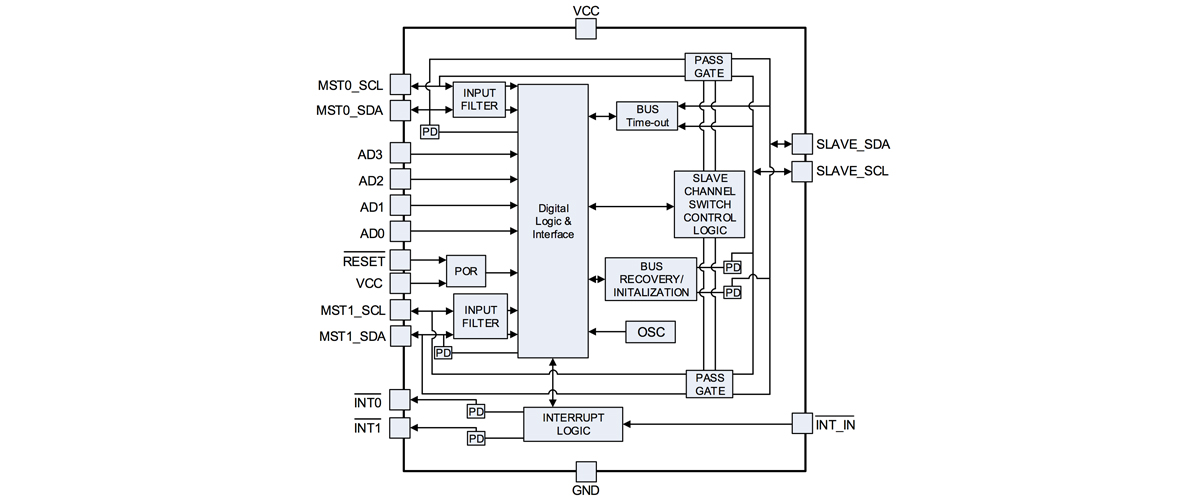

l 2-to-1 bidirectional master selector

l Channel selection via I2C-bus

l I2C-bus interface logic; compatible with SMBus standards

l 2 active LOW interrupt outputs to master controllers

l Active LOW reset input

l Software reset

l Four address pins allowing up to 112 different addresses

l Arbitration active when two masters try to take the downstream I2C-bus at the same time

l The winning master controls the downstream bus until it is done, if it is within the reserve time

l Bus time-out after 150 ms on an inactive downstream I2C-bus (optional)

l Readable device ID (manufacturer, device type, and revision)

l Bus initialization/recovery function

l Low Ron switches

l Allows voltage level translation between 1.8 V, 2.3 V, 2.5 V, 3.3 V and 3.6 V buses

l Software identical for both masters

l Operating power supply voltage range of 2.3 V to 3.6 V

l All I/O pins are 3.6 V tolerant

l Up to 1 MHz clock frequency